Mano의 컴퓨터시스템구조 제3판, 프로텍 미디어, 김종상 옮김 도서를 정리, 요약하는 글입니다.

1. 기본 컴퓨터의 설계

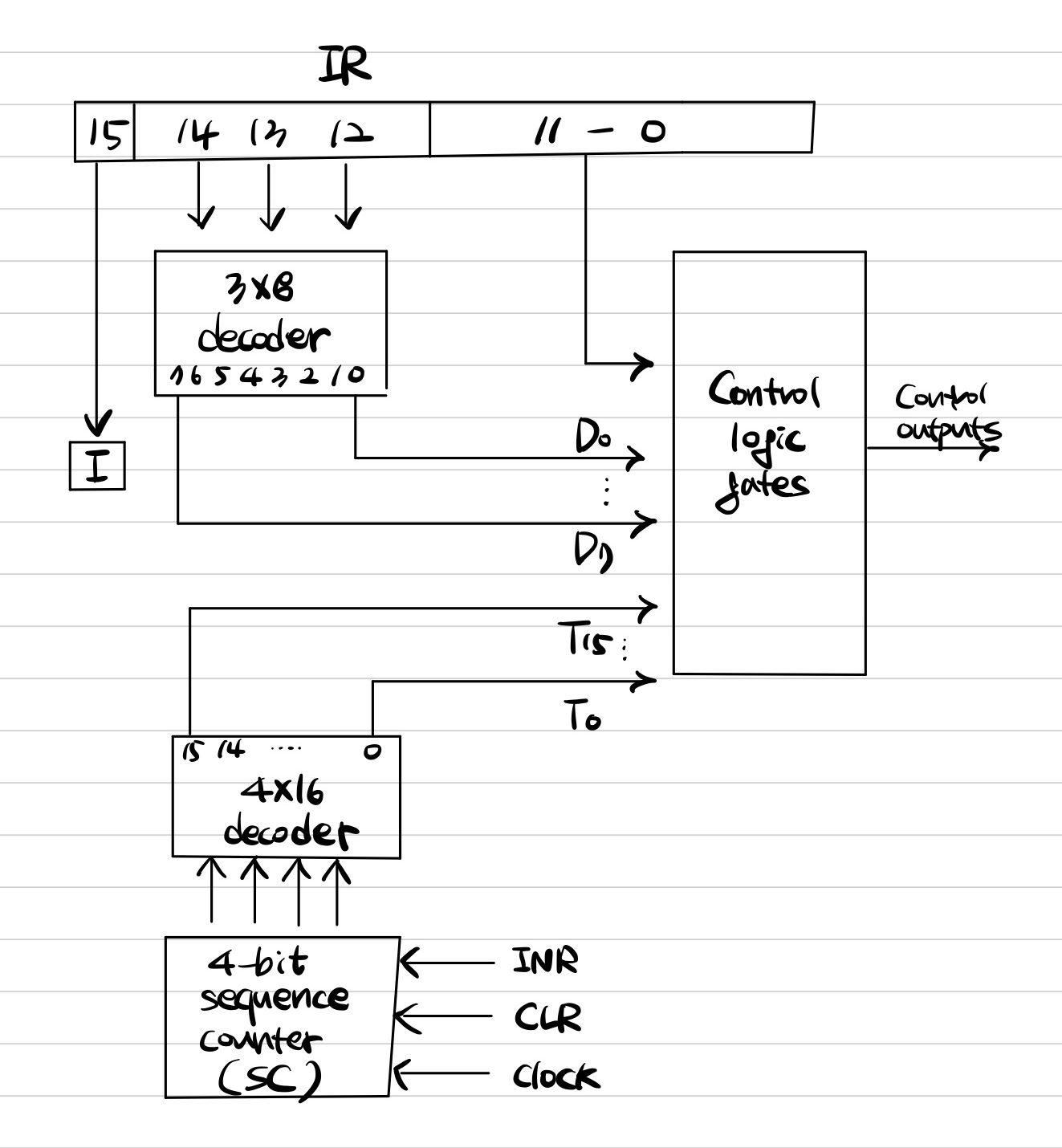

- 하드웨어 구성

(1) 4096 x 16 메모리

(2) 9개 레지스터 : AR, PC, DR, AC, IR, TR, OUTR, INPR, SC

(3) 7개의 플립플롭 : I, S, E, R, IEN, FGI, FGO

(4) 2개의 디코더 : 3x8 디코더, 4x16 디코더

(5) 16비트 공통 버스

(6) 제어 논리 게이트들

(7) AC 입력에 연결된 가산 논리 회로

2. 제어 논리 게이트

- 제어 논리 게이트는 컴퓨터가 명령어를 수행할 때 필요한 다양한 제어 신호를 생성하고 전달하는 역할을 한다.

- 입력 신호 : IR의 0~15비트, SC와 연결된 4x16 디코더, AC가 0인지 검사하기 위한 AC의 0~15비트, 부호를 검사하기 위한 AC(15)비트, DR이 0인지 검사하기 위한 0~15비트, 7개의 플립플롭 값 등

- 출력 신호 : 9개 레지스터 입력 제어 신호, 메모리 쓰기 및 읽기 제어 신호, 플립플롭 세트, 클리어, 보수 신호, 버스 선택(S0, S1, S2) 신호, AC에 대한 가산 논리 회로 제어 신호

3. 레지스터와 메모리에 대한 제어

- 레지스터의 제어 입력에는 LD(로드), INR(인크리트), CLR(클리어) 등이 연결된다.

- 예를 들어서 AR 레지스터의 제어 입력을 구성하는 게이트 구조를 만들고 싶다면, 먼저 AR의 내용을 변경시키는 마이크로 연산을 찾는다.

R'T0 : AR ← PC

R'T2 : AR ← IR(0-11)

D7'IT3 : AR ← M[AR]

RT0 : AR ← 0

D5T4: AR ← AR + 1

이렇게 찾은 제어 함수를 부울 함수식으로 만든다.

LD(AR) = R'T0 + R'T2 + D7'IT3

CLR(AR) = RT0

INR(AR) = D5T4

게이트 논리도는 위와 같다.

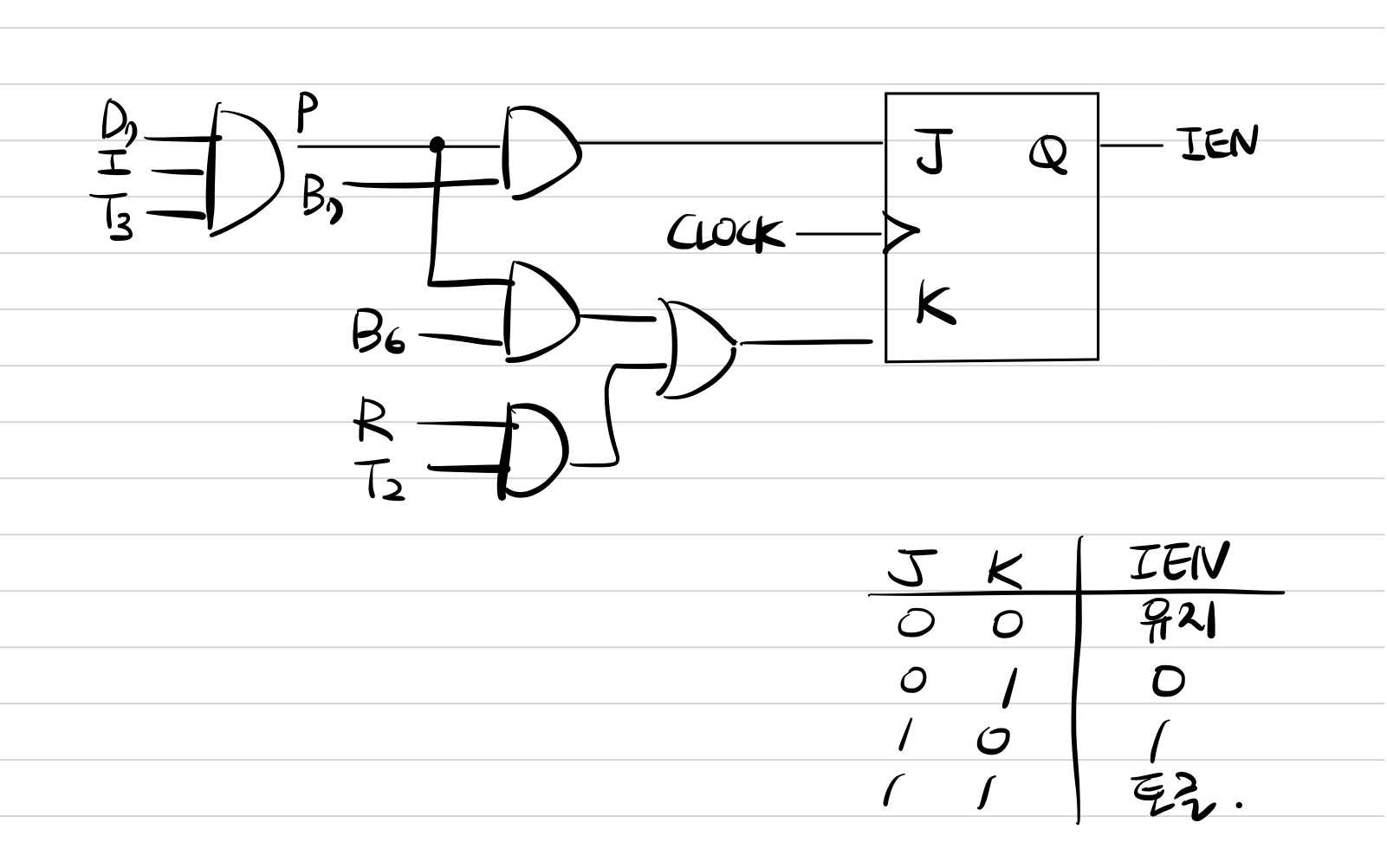

4. 단일 플립플롭에 대한 제어

- 레지스터 제어 입력과 마찬가지로, 플립플롭 값이 변하는 제어 함수를 찾아 부울 함수 식으로 바꾼다. 예를 들어, IEN 플립플롭의 값이 변하는 제어함수는 다음과 같다.

pB7 : IEN ← 1

pB6 : IEN ← 0

RT2 : IEN ← 0

여기서 p는 D7IT3를 나타내고 B7은 IR(6), B6는 IR(7)이다. 이를 JK 플립플롭으로 제어 게이트 논리를 구하면 다음과 같다.

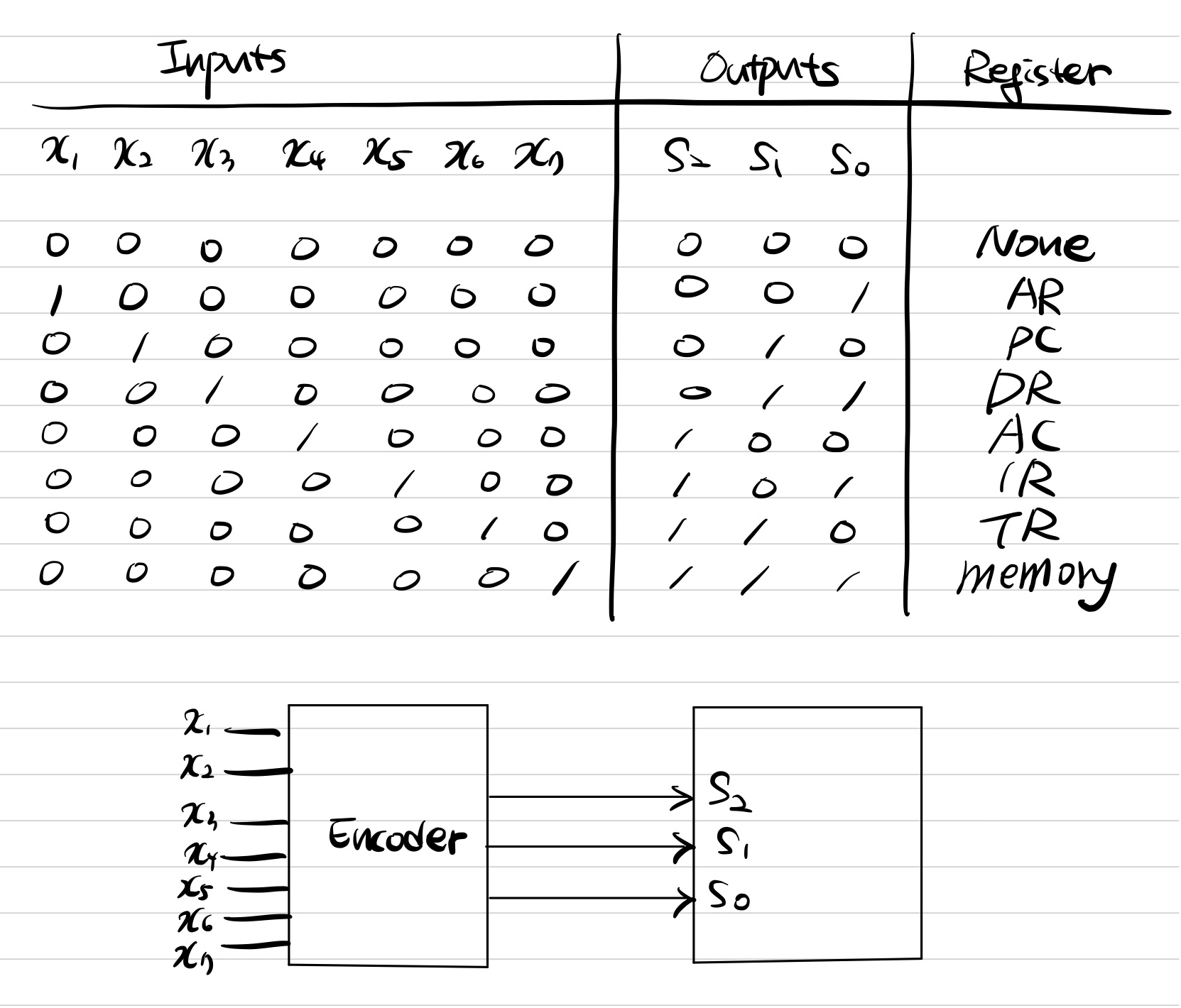

5. 공통 버스에 대한 제어

- 16비트 공통 버스의 선택 입력은 S2, S1, S0에 의해 제어된다. 이진 인코더의 진리표를 나타내어 인코더의 출력은 버스 선택 논리에 연결된다.

- 예를 들어 메모리 데이터 출력은 x7 = 1, S2S1S0 = 111 일때 선택되는데, 이에 대한 부울식은 다음과 같다.

x7 = R'T1 + D7'T3 + (D0 + D1 + D2 + D6)T4 이다.

메모리에 출력하는 마이크로 연산에 대한 자세한 내용은 아래와 같다.

R'T1 : IR ←M[AR]

D7'T3 : AR ←M[AR]

D0T4 : DR ← M[AR]

D1T4 : DR ← M[AR]

D2T4 : DR ← M[AR]

D6T4 : DR ← M[AR]

'CS > 컴퓨터구조(Mano)' 카테고리의 다른 글

| [컴퓨터구조] ch.8 중앙처리장치 (1) 스택 구조 (1) | 2024.10.09 |

|---|---|

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (11) 누산기 설계 (1) | 2024.10.09 |

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (9) 컴퓨터에 대한 완전한 기술 (0) | 2024.10.03 |

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (8) 입출력과 인터럽트 (2) | 2024.10.02 |

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (7) 메모리 참조 명령어 (0) | 2024.10.01 |