Mano의 컴퓨터시스템구조 제3판, 프로텍 미디어, 김종상 옮김 도서를 정리, 요약하는 글입니다.

1. 메모리 참조 명령어

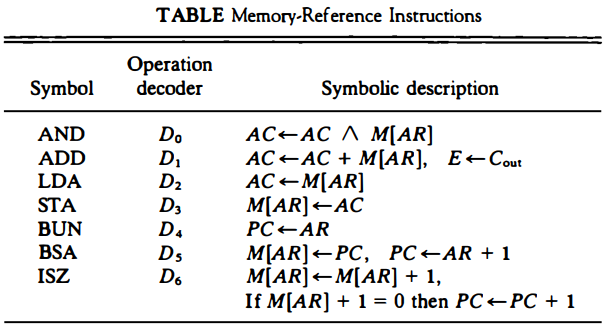

- 위는 7가지의 메모리 참조 명령어를 기술한 표이다.각 명령은 디코더의 출력 Di에 의해 구별된다.

- 피연산자에 대한 유효 주소를 찾아오는 것은 T2(I = 0일 때)나 T3(I = 1일 때) 시간에 AR 레지스터로 전송된다. (I = 1이면 간접 주소 방식이므로 한번 더 메모리의 유효 주소에 접근해야 하므로 T3 시간이 되어야 한다.) 명령의 수행은 T4 시간에 시작된다.

2. AND 명령어

D0T4 : DR ← M[AR]

D0T5 : AC ← AC∧DR, SC ← 0

- AC와 유효 주소로 지정된 메모리 워드의 각 비트쌍에 대해 AND 연산 수행 후, 결과값 AC에 전송한다.

- 메모리로부터 데이터를 가져와야 하므로 두 개의 명령이 같은 시간에 동시에 실행될 수는 없다.

3. ADD 명령어

D1T4 : DR ← M[AR]

D1T5 : AC ← AC + DR, E ← Cout, SC ← 0

- 유효 주소로 지정된 메모리 워드의 내용을 AC와 더한 다음, 그 합을 AC에 저장하고 출력 캐리(Cout)는 E 플립플랍에 전송한다.

4. LDA 명령어

D2T4 : DR ← M[AR]

D2T5 : AC ← DR, SC ← 0

- 유효 주소로 지정된 메모리 워드의 내용을 AC에 전송한다.

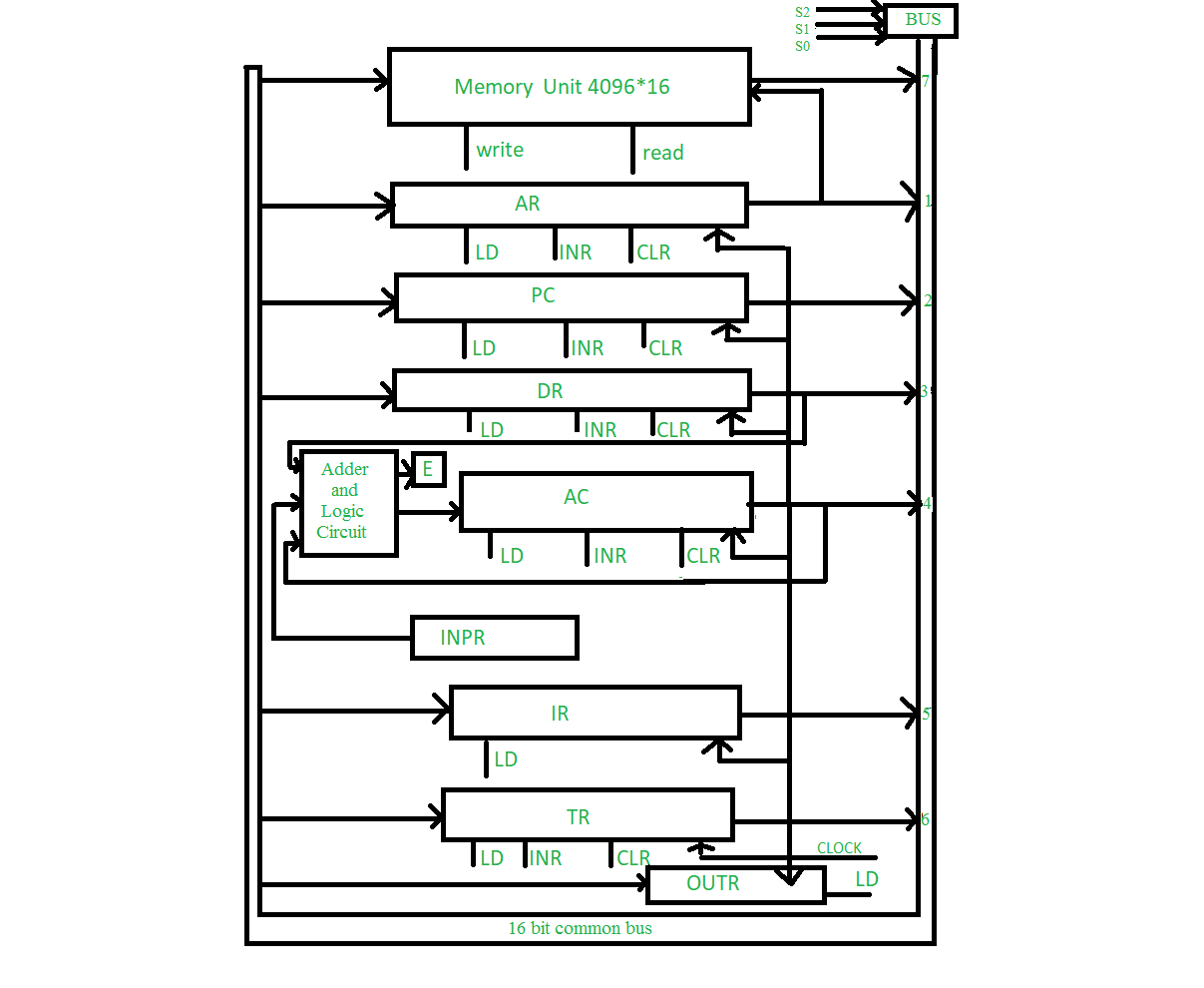

- 위의 사진을 다시 참고해보면, AC 레지스터와 직접 연결된 경로가 없다. 따라서 메모리의 내용을 DR에 담은 후 가산 논리 회로(Adder and Logic Circuit)를 통해서 AC로 전송할 수 있다. (DR의 출력은 가산 논리 회로와 연결되어 있다.)

- 버스 시스템에서는 가산 논리 회로에서의 지연을 막기 위해서 버스에서 AC와의 연결이 없다. 그렇기 때문에 원래 메모리에서 읽어온 데이터를 버스를 통해 전송하기 위하여 하나 이상의 클럭 사이클이 필요하다고 가정하면, 여기서는 각 마이크로 연산을 한 클럭 사이클에 수행되도록 구현할 수 있다.

5. STA 명령어

D3T4 : M[AR] ← AC, SC ← 0

- store AC라는 뜻으로, AC의 내용을 유효 주소로 지정된 메모리 워드에 전송한다. 즉 AC의 내용을 메모리에 저장한다.

- AC의 출력이 버스를 통해서 메모리에 입력되어 있으므로 한 번의 마이크로 연산으로 가능하다.

6. BUN 명령어

D4T4 : PC ← AR, SC ← 0

- BUN(Branch Unconditionally)는 무조건 분기한다는 뜻으로, 프로그램의 수행을 유효 주소로 지정된 명령어로 옮겨준다.

- AR의 유효 주소가 버스를 타고 PC로 전송되어 그 명령어가 fetch된다.

7. BSA 명령어

D5T4 : M[AR] ← PC, PC ← AR + 1

D5T5 : PC ← AR, SC ← 0

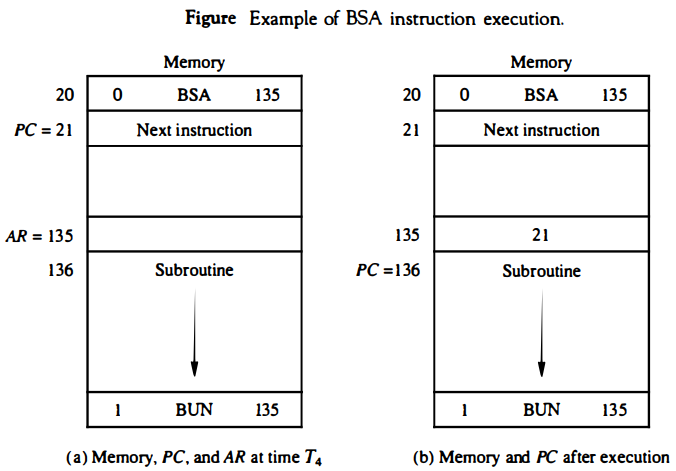

- BSA(Branch and Save Return Address)는 서브 루틴(프로시저) 분기라는 뜻으로, 현재 PC에 저장된 순서상의 다음 명령어 주소가 유효 주소로 지정된 메모리에 저장되고 유효 주소보다 1 큰 값이 PC로 전송되어 서브 루틴의 첫 번째 명령어를 가리키게 한다.

- 서브루틴 시작 명령어 바로 위에 돌아가야할 복귀 주소를 저장하고 분기를 시키는 것이다. 위 그림에서 왼쪽의 예를 보면, 현재 T4 일 때, PC = 21이고 AR = 135이다. M[135]에 21을 저장하고(서브 루틴 시작 주소 바로 위에 저장) PC에는 136을 전송한다. 서브루틴이 다 끝나면 맨 끝에 간접 BUN 명령어를 이용해 135에 저장된 21을 꺼내와 PC에 저장해 다음 명령을 수행한다. 하지만 대부분의 컴퓨터는 복귀 주소를 프로세서 레지스터나 스택에 저장한다.

8. ISZ 명령어

D6T4 : DR ← M[AR]

D6T5 : DR ← DR + 1

D6T6 : M[AR] ← DR, if(DR = 0) then (PC ← PC + 1), SC ← 0

- ISZ(increment and skip if zero)는 유효 주소로 지정된 워드의 값을 1 증가시키고, 증가된 값이 0이면 PC도 증가시켜 다음 명령어를 수행하게 하는 것이다.

- ISZ는 for 반복문과 같은 구조에서 많이 쓰이는 분기문이다. 레지스터 DR의 값을 계속 증가시키다가 만약 0이 되면 빠져나와서 분기하는 것과 비슷하다.

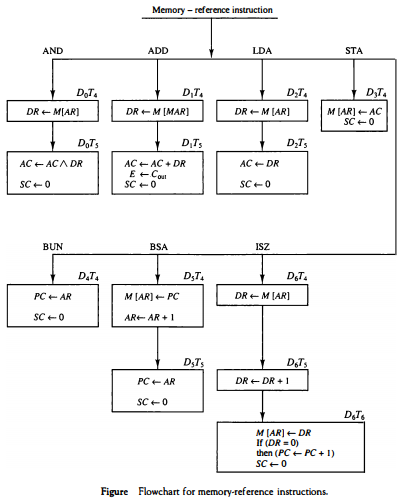

9. 제어 흐름도

- 앞서 살펴본 7가지의 메모리 참조 명령어에 해당하는 마이크로 연산들을 보여주는 전체 흐름도이다.

- 이 흐름도의 경우에 순차 카운트는 3bit로 만들어야 할 것이다. 가장 긴 명령어인 ISZ가 T6에 끝나기 때문에 T0~T6까지 7개의 타이밍 신호가 필요하기 때문이다.

'CS > 컴퓨터구조(Mano)' 카테고리의 다른 글

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (9) 컴퓨터에 대한 완전한 기술 (0) | 2024.10.03 |

|---|---|

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (8) 입출력과 인터럽트 (2) | 2024.10.02 |

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (6) 명령어 종류와 결정 (1) | 2024.10.01 |

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (5) 명령어 사이클 (fetch, decode) (0) | 2024.10.01 |

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (4) 타이밍과 제어 (0) | 2024.10.01 |