Mano의 컴퓨터시스템구조 제3판, 프로텍 미디어, 김종상 옮김 도서를 정리, 요약하는 글입니다.

1. 컴퓨터 레지스터

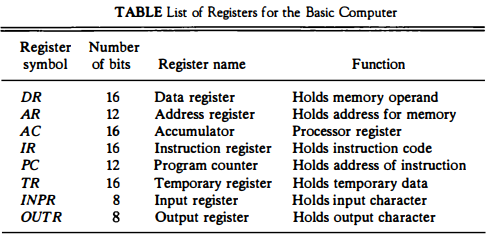

- 컴퓨터에는 다양한 레지스터가 필요하다. 아래 표에 기본 컴퓨터에 필요한 레지스터가 있다.

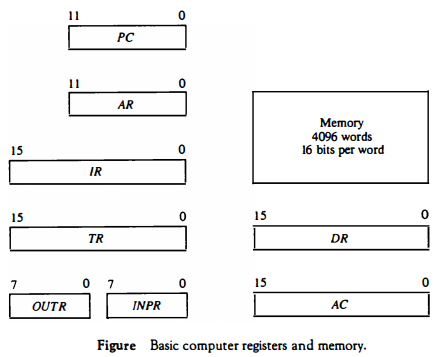

- 이 책에서 설정한 컴퓨터의 메모리는 4096 x 16 bit로 한 칸의 크기가 16bit인 메모리가 4096개 있다는 뜻과 같다. 명령어 코드에서 피연산자 주소를 표현하기 위해서는 12 bit가 필요하다. 4096(=212)개의 메모리를 지정하기 위해서이다. 전체 16bit인 명령어 코드에서 주소가 12bit를 차지하면 남은 4bit 중 1bit는 직간접 주소를 나타내는데 쓰인다. 남은 3bit가 명령어 코드를 나타낸다.

- 많은 레지스터 중에서 크기가 16bit인 레지스터는 메모리에서 읽어온 명령어를 담는 레지스터인 IR, 계산 도중의 데이터를 담는 TR, 메모리에서 읽어온 피연산자를 저장하는 DR, 누산기 레지스터인 AR이다.

- 레지스터 크기가 12bit인 레지스터는 메모리의 주소를 나타내는 레지스터일 경우 해당된다. 여기서는 메모리 주소 레지스터인 AR, 프로그램 카운터 PC이다. PC는 다음에 실행될 명령어의 주소를 지정하고 있다.

- 이 밖의 입출력 장치로부터 송수신하는 INPR, OUTR이 있다.

2. 공통 버스 시스템

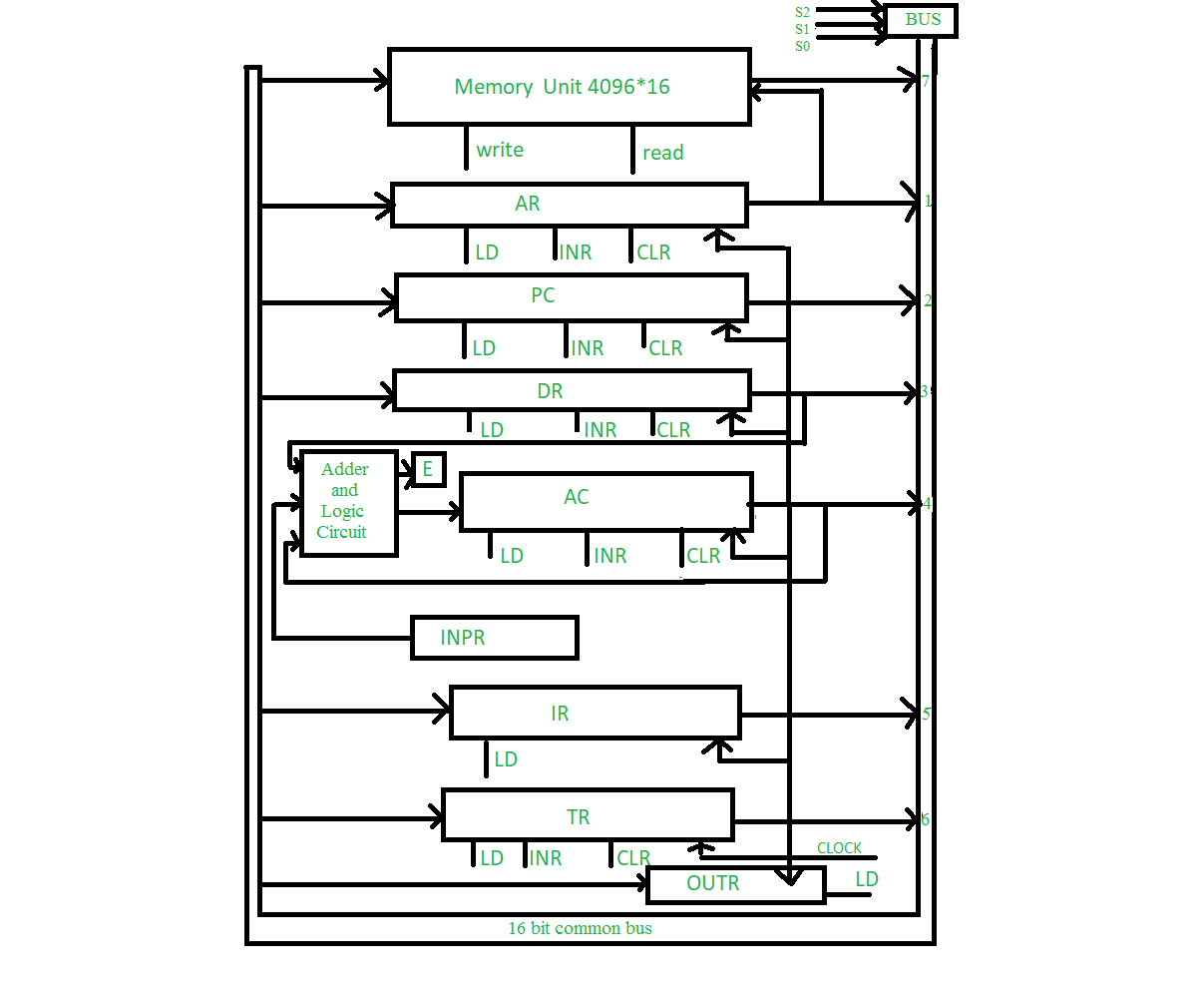

- 기본 컴퓨터에는 레지스터들 사이나 레지스터와 메모리 사이에 정보 전송을 하기 위한 경로(path)가 제공되어야 한다. 아래 그림은 레지스터와 메모리를 공통 버스 시스템으로 연결하는 방법으로 구성한다.

- 레지스터와 메모리를 공통 버스 시스템으로 연결하는 방법으로 7개의 레지스터와 메모리의 출력이 공통 버스에 연결되어 있고, 선택 입력 S2, S1, S0를 통해서 놓이게 될 출력을 선택한다.

- 각 레지스터는 LD(로드) 입력이 인에이블 되어있는 레지스터가 다음 클럭 펄스에서 버스의 데이터를 받아서 저장한다. 메모리는 쓰기 입력이 활성화 되었을 때 버스의 내용을 받을 수 있다.

- 12비트 AR과 PC의 내용이 버스에 전송될 때 상위 4비트가 0으로 채워지며, 버스의 내용이 AR이나 PC에 전송될 때는 하위 12비트만 전송된다. 8비트인 레지스터 INPR, OURT은 하위 8비트만 버스와 주고 받으며, INPR은 입력 장치로부터 한 문자를 읽어와 AC로 전송하며, OUTR은 AC로부터 한 문자를 읽어와 출력 장치로 전송한다.

- AR, PC, DR, AC, IR, TR 총 6개의 레지스터는 모두 공통 버스에 입출력이 연결되어 있다. IR을 제외하고 남은 5개의 레지스터는 모두 LD, INC, CLR등의 제어를 가지고 있고 IR은 LD 제어만 가지고 있다. IR은 단순히 명령어를 읽어오기만 하기 때문에 INC, CLR가 필요하지 않다. 메모리에도 공통 버스에 입출력이 연결되어 있어 Write 동작을 통해서 레지스터의 내용을 메모리에 전송할 수 있고, Read 동작으로 메모리의 데이터를 읽어올 수 있다.

- 메모리에는 AR에 별도로 연결되어 있다. 또한 AR은 다른 5개의 레지스터와 연결되어 있다. 즉 AR은 메모리의 주소를 지정하는 레지스터이므로 메모리에는 AR을 써서 별도의 버스를 타지 않고도 주소 데이터를 전송할 수 있다. 또한 AC는 유일하게 버스의 입력이 없어서 메모리의 데이터를 읽어올 수 없다.

- AC는 Adder and Logic Circuit이라는 가산 논리 회로가 입력으로 연결되어 있는데 여기는 총 세가지의 입력이 있다. 첫번째는 AC를 보수화 하고 시프트 하기 위한 AC 출력에 연결, 두번째는 DR의 출력에 연결, 세번째는 입력 레지스터 INPR에 연결되어 있다. DR에 연결된 입력은 산술 연산 결과를 AC에 전송하고 캐리를 담는 E 플립플롭으로 전송한다. 이렇게 연결되어 있기 때문에 레지스터의 내용이 버스를 타고 출력되는 것과 동일한 클럭에, 논리 회로 연산이 수행되고 버스의 데이터가 목적 레지스터로 버스를 타고 가거나, 가산 논리 회로의 출력으로 AC의 입력이 가능하다. 즉 DR←AC, AC←DR 이 두 마이크로 연산은 한 번의 동일한 클럭에 연산이 가능하다는 것이다. 예를 들어, S2S1S0 = 100으로 설정하면 AC 내용이 4번 버스를 타고 올라와 있고, DR의 LD 입력을 인에이블하면 동일한 클럭에서 DR의 내용을 AC에 전달 가능하다.

'CS > 컴퓨터구조(Mano)' 카테고리의 다른 글

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (4) 타이밍과 제어 (0) | 2024.10.01 |

|---|---|

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (3) 컴퓨터 명령어 (0) | 2024.10.01 |

| [컴퓨터구조] ch.5 기본 컴퓨터의 구조와 설계 (1) 명령어 코드 (0) | 2024.09.22 |

| [컴퓨터구조] ch.4 레지스터 전송과 마이크로 연산 (4) 시프트 마이크로 연산 (0) | 2024.09.22 |

| [컴퓨터구조] ch.4 레지스터 전송과 마이크로 연산 (3) 논리 마이크로 연산 (0) | 2024.09.20 |